计组试卷

此试卷为软院2010年计算机组成试卷

I. 单选题(每题2分)

- A 2’s-complement overflow cannot occur when

- A. two positive numbers are added

- B. two negative numbers are added

- C. a positive number is added to a negative number

- D. a positive number is subtracted from a negative number

C

- What is the effect of the following instruction? move ecx, [ebp + 8]

- A. Add 8 to the contents of ebp and store the sum in ecx.

- B. Add 8 to the contents of ebp, treat the sum as a memory address and store the contents at that address in ecx.

- C. Add & to the contents of the memory location whose address is stored in ebp and store the sum in ecx

- D. Add the contents of ebp to the contents of memory address 8 and store the sum in ecx.

B

Answer the question 3 - 4 based on the following information:

A memory system uses 24 - bit physical address. It has a direct - mapped cache with 64 entries. The block size is 4 words (word size is 4 bytes). Each cache entry has a “valid bit”, a “tag field”, and space for data.

- The number of bits reserved for the tag field is

- A. 14

- B. 10

- C. 6

- D. 12

A

- The total number of bits in the cache is

- A. $2^{6*(14 + 3)}$

- B. $2^{6*(3 + 3)}$

- C. $2^{8*(14 + 5)}$

- D. $2^{14(3 + 3)}$ A*

- As part of handling interrupts, the processor must inform the device that its request has been recognized. This may be accomplished by means of a special control signal:—-signal.

- A. interrupt - enable

- B. interrupt - acknowledge

- C. interrupt - request

- D. interrupt - service

B

- In IEEE 754 double - precision floating point number standard, instead of the signed exponent, E, the value actually stored in the exponent field is an unsigned integer

- A. $E’ = E + 127$

- B. $E’ = E + 128$

- C. $E’ = E + 1023$

- D. $E’ = E + 1024$

C

- The microroutines for all instructions in the instruction set of a computer are stored in a special memory called the

- A. flash memory

- B. control store

- C. uPC

- D. SRAM

B

- In DMA transfers, the data transfer unit between main memory and /O devices is

- A. byte

- B. word

- C. block of data

- D. bit

C

- arise from resource conflicts when the hardware cannot support all possible combinations of instructions simultaneously in overlapped execution.

- A. Structural hazards

- B. Data hazards

- C. Control hazards

- D. Branch hazards

A

- In microprogram - controlled machines, the relationship between the machine instruction and the microinstruction is

- A. a machine instruction is executed by a microinstruction

- B. a microinstruciton is composed of several machine instructions

- C. a machine instruction is interpreted by a microroutine composed of microinstructions

- D. a microroutine is executed by a machine instruction

C

- In memory - mapped I/O system, we use to differentiate memory locations and I/O devices.

- A. different addresses

- B. different address buses

- C. different instructions

- D. different control signals

D

- A major advantage of direct mapping of a cache is its simplicity. The main disadvantage of this organization is that.

- A. It’s more expensive than other types of cache organization.

- B. Its access time is greater than that of other cache organizations.

- C. The cache hit ratio is degraded if two or more blocks used alternatively mapped onto the same block frame in the cache.

- D. It does not allow simultaneously access to the intended data and its tag.

C

- Assume that the multiplicand is 110011 and the multiplier is 101100. If multiply them using the Booth algorithm, then the Booth recoding multiplier is.

- A. - 1 + 10 - 110

- B. – 1 – 10 – 100

- C. - 1 + 10 - 100

- D. + 1 + 10 - 100

C

- If the 2006 version of a computer executes a program in 200s and the version of the computer made in the year 2007 executes the same program in 150s, then the speedup that the manufacturer has achieved over the two - year period is.

- A. 1.44

- B. 1.78

- C. 1.63

- D. 1.33

D

- Assume that a Branch instruction uses relative addressing mode. It is two bytes in length. The first byte contains opcode, and the second contains offset (2’s - complement representation). Assume that when the processor fetches the first byte of Branch instruction, PC points to the next instruction automatically. At first $(PC)=2008H$ (before fetching the Brach instruction), if the program wants to jump to the address of 2001H, then the content of the second byte of this Branch instruction is

- A. 07H

- B. F7H

- C. 09H

- D. F9H

D

Which one of the following about one-address instruction is true?

- A. One-address instruction has only one operand

- B.One-address instruction may have one operand or two operands

- C. One-address instruction has two operands, and the other operand is provided implicitly

D.One-address instruction may have three operands, and the other two operand are provided implicitly

B

CPU responses the interrupt requestA. after it completes its fetch cycle

- B. after it completes its execution cycle

- C.when the interrupt source issues the interrupt request

D.when the bus is not busy

C

The advantage of carry-lookahead adder is__.A. Optimize the structure of the adder

- B. Save hardware parts

- C. Accelerate the generation of the carries

- D. Augment the structure of the adder

C

In microprogram-controlled machines, the relationship between the machine instruction and the microinstruction is__.

- A. a machine instruction is executed by a microinstruction

- B. a microinstruciton is composed of several machine instructions

- C. a machine instruction is interpreted by a microroutine composed of microinstructions

D. a microroutine is executed by a machine instruction

C

Once the DMA controller obtains access to the system bus, it transfers one byte of data and then returns the control of system to the processor. This DMA transfer mode is_.A. Burst Mode

- B. Block Mode

- C. Cycle Stealing Mode

- D. Transparent Mode

C

- Assume that the capacity of a kind of SRAM chip is 16K×32, so the sum of address lines and data lines of this chip is__.

- A. 48

- B. 46

- C. 36

- D. 32

B

- Assume that the multiplicand is 110011 and the multiplier is 101110. If multiply them using the Booth algorithm, then the Booth recoding multiplier is__.

- A. – 1 – 1 0 0 – 1 0

- B. + 1 – 1 0 0 + 1 0

- C. – 1 + 1 0 0 – 1 0

- D. 1 + 1 0 0 – 1 0

B

- The microroutines for all instructions in the instruction set of a computer are stored in the.

- A. memory controller

- B. main memory

- C. control store

- D. cache

C

__ is the process by which the next device to become the bus master is selected and bus mastership is transferred to it.

- A. Bus protocol

- B. Bus arbitration

- C. Bus timing

- D. Bus transceiver

B

—- has/have external fragmentation problem.

- A. Paging

- B. Segmentation

- C. Segmentation with paging

- D. Segmentation and segmentation with paging

D

The range and accuracy of floating-point numbers depend on__ respectively.

- A. The size of exponent and the representation of mantissa

- B. The size of exponent and the size of mantissa

- C. The size of mantissa and the representation of exponent

- D. The size of mantissa and the size of exponent

A

In a synchronous bus, controlling of data transfer on the bus is based on __.

- A. a common clock signal only

- B. a handshake signal only

- C. both clock signal and handshake signal

- D. either clock signal or handshake signal

A

Which one of the following is not used to prevent data hazards? ___

- What is the difference between a subroutine and an interrupt - service routine?

子程序:由当前执行的程序调用,处理器可能预先知道会修改哪些内容;中断服务程序:由IO设备调用,处理器并不知道会对哪里修改,因此要保存所有重要的信息 What are the advantages and disadvantages of hardwired and microprogrammed control?

硬件控制:优点:速度快;缺点:成本高,实现复杂,对电路要求高

微程序控制:优点:灵活性高,成本低;缺点:速度慢Explain the drawback of the ripple carry full adder when you need to design 64 - bit CPU core. And give a solution for the drawback. (Just give a name of the circuit. You don’t need to draw a circuit of solution).

64位的行波进位加法器需要127个周期得到所有的求和结果,128个周期得到所有的进位结果- A system has 48 - bit virtual addresses and 36 - bit physical addresses. If the system uses 4096 - byte pages, how many virtual and physical pages can the address space support?

页大小为4KB,物理地址36位,能访问$2^{24}$个物理页;虚拟地址48位,能访问$2^{36}$个虚拟页 - What is the difference between DRAM and SRAM, in terms of characteristics such as speed, size, cost and application?

速度:DRAM<SRAM

大小:DRAM>SRAM

成本:DRAM<SRAM

应用:DRAM用于主存,SRAM用于寄存器和高速缓存 In what circumstance will arithmetic overflow occur when two integers represented by 2’s complement form are added? And write out the logic expression to detect overflow.

当两个数的符号相同,但结果的符号与其不同,则发生溢出

$Overflow =x_{n-1} y_{n-1} \overline{S}_{n-1}+\overline{x}_{n-1} \overline{y}_{n-1} s_{n-1}=c_{n} \oplus c_{n-1}$Describe the process of interrupt processing.

IO设备发出中断请求,处理器收到中断请求,若处理器的IE为0,则不接受此中断请求;否则比较优先级后,将自身的IE位置为1,查询中断向量表,将自身的优先级提升到此中断,在向此IO设备发送中断确认信号,存储PC和PSW后进入中断服务程序,执行完毕后恢复存储的信息,IE置为0

III. 综合题(每题10分)

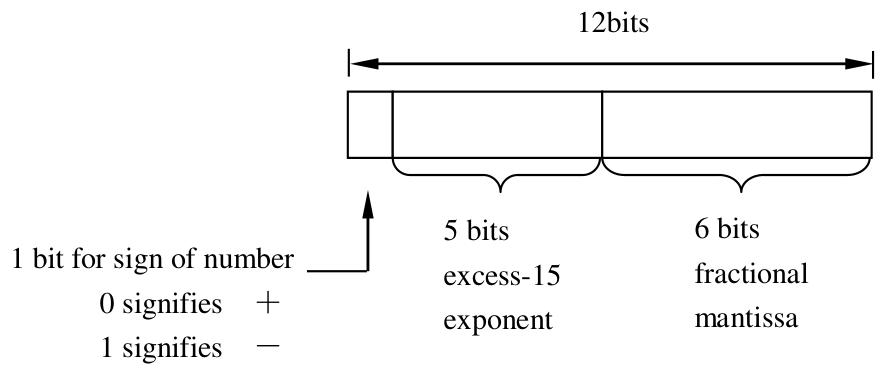

- what are the largest positive and the smalist positive numbers representable in this format? Note: Using rounding as the truncation method in the answers. Write the computation process!

指数位有3位,表示0~31的无符号数。若排除无穷大(e=31)和0(e=0),则最大正数为$+(2-2^{-6}\times10^{15})$,最小正数为$+2^{-6}\times10^{-14}$

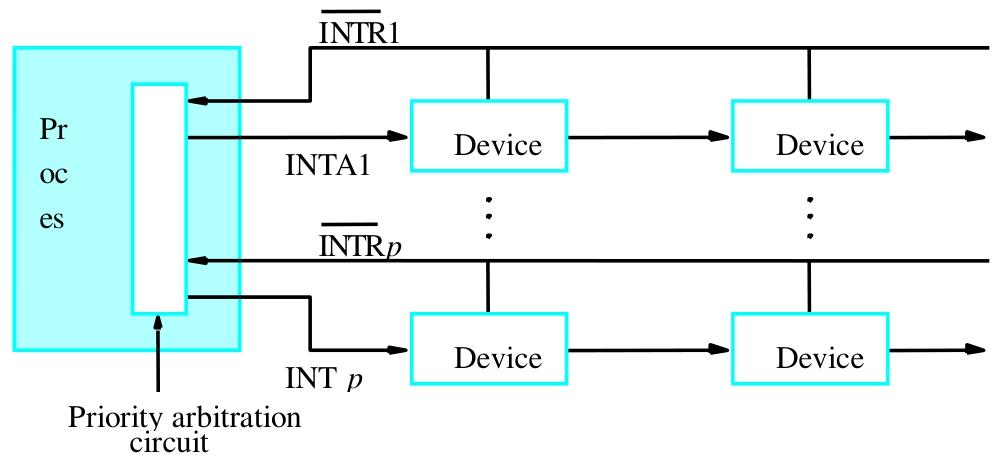

- A logic circuit is needed to implement the priority network shown like figure 2. The network handles three interrupt request lines. When a request is received on line INTRi, the network generates an acknowledgement on line INTAi. If more than one request is received, only the highest - priority request is acknowledged, where the ordering of priority is: priority of INTR1 > priority of INTR2 > priority of INTR3.

- (1) Give a truth table for each of the outputs INTA1, INTA2, and INTA3.

- (2) Give logic expressions of INTA1, INTA2, INTA3 and a logic circuit for implementing this priority network.

| $\overline{INTR1}$ | $\overline{INTR2}$ | $\overline{INTR3}$ | $INTA_1$ | $INTA_2$ | $INTA_3$ |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | x | 0 | 1 | 0 |

| 1 | x | x | 1 | 0 | 0 |

$INTA_1=\overline{INTR1}$

$INTA_2=\overline{INTR2}.INTR1$

$INTA_1=\overline{INTR3}.INTR1.INTR2$

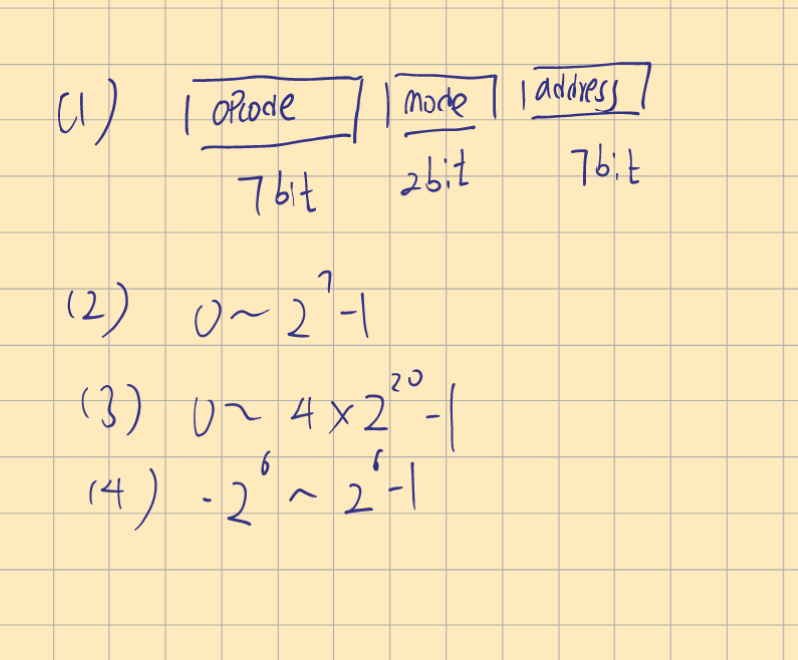

- Assume that a computer’s word - length is 16 - bit, the capacity of main memory is 64K words. If it employs single - word - length one - address instructions and contains 64 instructions. Design an instruction format with addressing modes of direct, indirect, index, and relative

包含64个指令,即分配6位表示opcode;四种模式,则分配两位表示模式;剩下的16-6-2=8表示address

- The following figure 3 gives part of the microinstruction sequence corresponding to one of the machine instructions of a microprogrammed computer. Microinstruction B is followed by C, E, F, or I, depending on bits b6 and b5 of the machine instruction register. Compare the two possible implementations described below.

- (1) Microinstruction sequencing is accomplished by means of a microprogram counter. Branching is achieved by microinstructions of the form: $b_{6}b_{5}$ branch to x, where $b_{6}b_{5}$ is the branch condition and X is the branch address.

- (2) Same as (1) except that the branch microinstruction has the form: Branch to x, OR Where X is a base branch address. The branch address is modified by bit - ORing of bits $b_{5}$ and $b_{6}$ with the appropriate bits with X

1.对小型计算机,Branch的转移地址不多且固定时更合适。这种方法缩短了指令的长度,提高了执行速度,但增大了设计的开销

2.对大型计算机而言,这种方法更灵活,电路实现更简单,成本更低,但速度慢

Consider the following piece of code:

int $x = 0$ int x = 0, y = 0; //The compiler puts x in R1 and y in R2.

int i; //The compiler puts i in R3.

int A[4096]; //A is in memory.

for (i = 0; i < 1024; i ++) { $x += A[i];$ }

for (i = 0; i < 1024; i ++) { $y += A[i + 2048];$ }

Assume that the system has a 8192 - byte, direct - mapped data cache with 16 - byte blocks.

假设主存中数据按行存储。缓存大小8KB,每个块的大小16B,则缓存中共存在512个块。若一个int占4个字节,则一个块能容纳4个int

使用直接映射,则每四个int需要一个载入一个块

第一个循环发生256次失效,第二个循环同样发生256次失效Using nonrestoring division algorithm, perform the operations A÷B on the 5-bit unsigned numbers $A=10101$ and $B=00101$ .Write the computation processes in a computer machine.

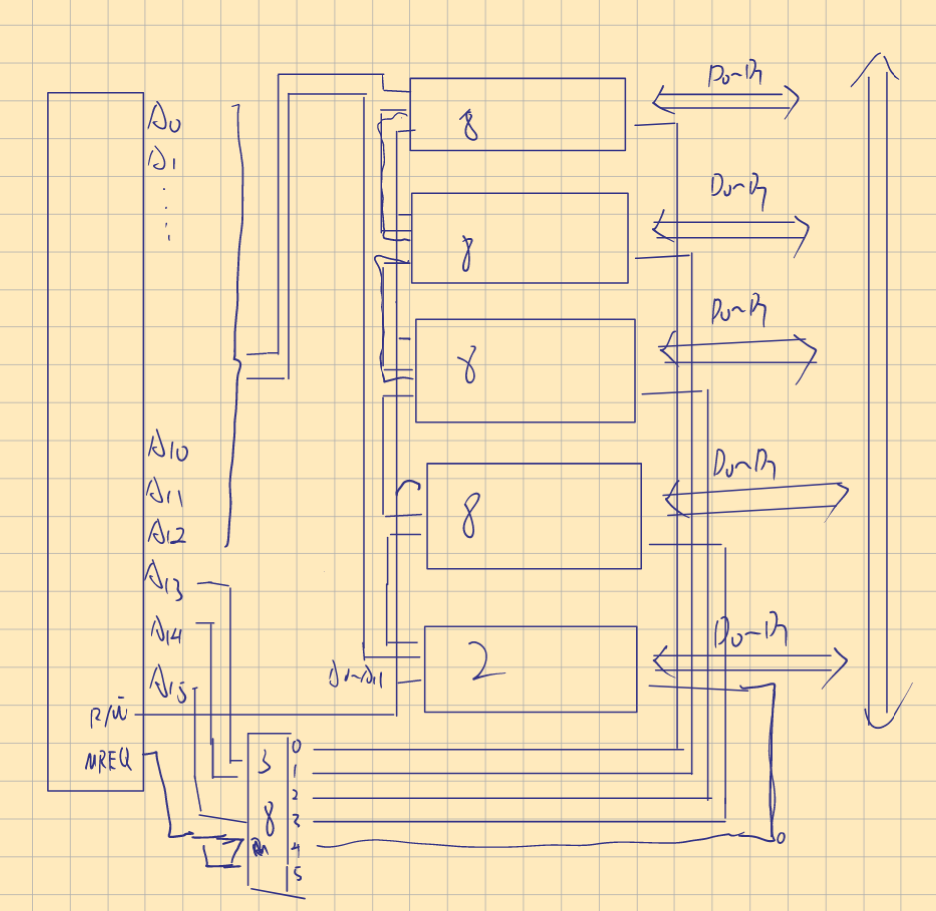

A byte-addressable computer has 16 address lines, 8 data lines, WR signal (\overline{WR}) signal (read/write control signal) and MREQ signal (access memory control signal). Its address space includes:

- a) system program area ranging from 0 to 8191(decimal)

- b) user program area ranging from 8192 to 32767(decimal)

- c) and the last 2K address space for system program working area

- There are some memory chips: ROM: 8K×8 SRAM: 16K×1, 2K×8, 4K×8, 8K×8

- (1) Please specify how many chips to select to design the main memory of the computer.

- (2) Draw the logic structure figure of the main memory, and the connection between the main memory and CPU.

Consider a computer with 4M×16 memory contains 97 instructions in its instruction set. The opcode length is fixed, and the addressing modes are direct, indirect, immediate, index, and relative. (Assume that the instruction length equals to word length)

(1) Draw the figure of one-address instruction format, and specify the function of each field.

(2) Specify the max range of the direct addressing mode. (in decimal)

(3) Specify the addressing range of one-level indirect addressing mode. (in decimal)

(4) Specify the offset of the relative addressing mode. (in decimal)